In fast allen elektronischen Geräten sind heute Mikrochips verbaut, die ihre Funktionen steuern: in der Telekommunikation, in der Sensorik, in Bordcomputern, aber auch in Liften, Bohrern, Toastern und vielem mehr. Den Weg vom Chipdesign bis zum Einbau in die Geräte vergleicht Thomas Lorünser, CEO von Photeon Technologies, mit dem Bau eines Hauses: „Wenn ich mein Traumhaus bauen will, arbeite ich mit einem Architekten zusammen. Mit ihm bespreche ich, wie das Grundstück am besten genutzt werden kann, welche Art von Haus ich will, welche Räume ich benötige und welche Techniken und Materialien zum Einsatz kommen sollen.“ Ähnlich wie der Architekt mit diesen Infos die passenden Bau- und Detailpläne zeichne, sei es auch bei der Entwicklung von Mikrochips.

„Unsere hochqualifizierten Ingenieure entwickeln – perfekt auf den Kundenwunsch zugeschnitten – das komplexe Chipdesign als Basis für die Herstellung von Silizium-Wafern“, erklärt der Manager. Photeon Technologies mit Firmensitzen in Dornbirn und nahe Mailand ist weltweit führend in der Chipentwicklung für sogenannte ASICs (Application-Specific Integrated Circuits), für die je nach Kundenanforderung die entsprechenden Schaltkreise entwickelt werden. Zu den Abnehmern dieser Chiplösungen zählen neben mittelständischen Unternehmen aus Zentraleuropa vor allem weltweit führende Konzerne in der Automobilelektronik, im Consumer- und im Kommunikationsbereich. Details zu den Kunden können aus Vertraulichkeitsgründen nicht genannt werden.

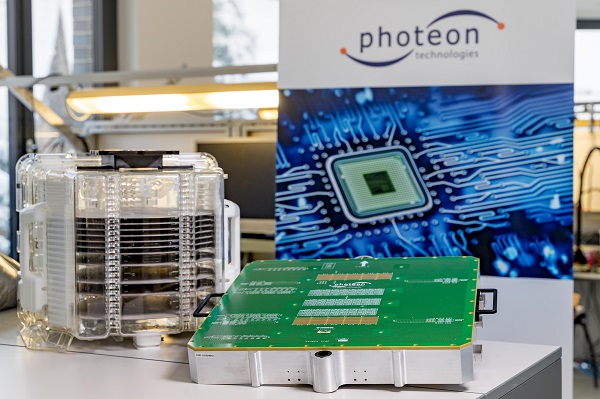

Hightech-Geräte zur Funktionsprüfung angeschafft

Zeichnete Photeon früher ausschließlich für das Chipdesign verantwortlich, wurde jetzt der nächste Schritt gemacht. Unterstützt durch eine EFRE-Förderung der EU wurden zwei Hightech-Geräte zur Funktionsprüfung der Chip-Rohlinge (Wafer) im Millionenwert angeschafft: „So haben wir weitere Teile der Wertschöpfung ins Haus geholt und entsprechendes Know-how aufgebaut“, erläutert Lorünser. Die EU-Förderung habe die Entscheidung für die Millionen-Investition entsprechend erleichtert. „Dadurch können wir nunmehr auch die Testprogramme für unsere Chips selber entwickeln, auf Waferebene validieren und in einem Temperaturbereich von minus 60 Grad bis 200 Grad Celsius charakterisieren.“ Dieser Schritt ermögliche es, auch Kleinserien selbst zu testen, um den Kunden schnellstmöglich getestetes Prototypenmaterial zur Verfügung zu stellen.

Damit habe Photeon den Sprung vom reinen ASIC-Entwickler zu einem Fabless-Halbleiter-Unternehmen perfekt gemeistert, freut sich Lorünser. Mit der technischen Innovation war und ist es allerdings nicht getan – auch das internationale Mitarbeiter-Team wurde durch weitere Experten aufgestockt. So gelang es beispielsweise, den Lead Engineer für die Testentwicklung von einem führenden europäischen Chiphersteller in das Photeon-Team zu holen. Auch die Ausbildung von Nachwuchs-Fachkräften nimmt Photeon jetzt selbst in die Hand. Wobei die Nähe zur Fachhochschule am Headquarter in Dornbirn entsprechend genutzt wird.

Testprogramm hilft Fehler zu vermeiden

Je nach Größe sind einige tausend bis mehrere 10.000 ASIC auf einem Silizium-Wafer von der Größe einer Pizza aufgebracht – und jeder einzelne muss gründlich geprüft werden. Toleranz für Fehler gibt es keine. Deswegen ist die hausinterne Testprogrammentwicklung derart wichtig. Da bei den Produktionspartnern die identen Testgeräte zum Einsatz kommen, kann das Programm für die sorgfältige Prüfung direkt von Photeon zur Verfügung gestellt werden: „Die Schwierigkeit liegt darin, das Testprogramm genau auf das Set-up abzustimmen. Die Testumgebung muss den realen Bedingungen beim Produktionspartner 1:1 entsprechen.“ Zu verbessern gebe es immer etwas und so werden die Testprogramme auch für bereits in Serienproduktion befindliche Chips immer weiterentwickelt und optimiert.

Die angeschafften Geräte sind bereits sehr gut ausgelastet und der CEO kann sich vorstellen, dass noch weitere Investitionen umgesetzt werden: „Die Qualität unseres Endproduktes hat sich noch einmal deutlich verbessert, obwohl die Toleranz schon davor sehr gering war. Auch bei bestehenden ASICs können wir Fehlermöglichkeiten ausschließen und Fortschritte machen, weil wir Testprogramme verfeinert haben. Das schafft neue und engere Kundenbeziehungen. Wir liefern höhere Qualität, schneller, flexibler und mit kürzeren Testzeiten“, so Lorünser abschließend.